# Low-Power Long Range 433/868 MHz LoRa® Technology Transceiver Module

#### **General Features**

- On-Board LoRaWAN™ Protocol Stack

- ASCII Command Interface over UART.

- Compact Form Factor: only 14.4x14.4x2.2 mm.

- European R&TTE Directive Assessed Radio Module.

- Single Operating Voltage: 1.8V to 3.6V.

- Temperature Range: -40°C to +85°C.

- Low-Power Consumption.

- Programmable RF Communication Bit.Rate up to 300 kbps with FSK Modulation, 10937 bps with LoRa® Technology Modulation.

- Integrated MCU, Crystal, Radio Transceiver with Analog Front End, Matching Circuitry.

- 10 GPIOs shared with 2 Analog Inputs.

# **RF/Analog Features**

- Low-Power Long Range Transceiver Operating in the 433 MHz and 868 MHz Frequency Bands.

- High Receiver Sensitivity: Down to -146 dBm.

- TX Power: Adjustable up to +17 dBm high

- Efficiency PA

- FSK, GFSK, and LoRa Technology Modulation

- Up to 15 km Coverage at Suburban and up to 5 km Coverage at Urban Area

### **Description**

The BIT48LR Low-Power Long Range LoRa

Technology Transceiver module provides an easy to use, low-power solution for long range wireless data transmission. The advanced command interface offers rapid time to market.

The BIT48LR module complies with the LoRaWAN Class A protocol specifications. It integrates RF, a baseband controller, command Application Programming Interface (API) processor, making it a complete long range solution.

The BIT48LR module is suitable for simple long range sensor applications with external host MCU.

### **Applications**

- Automated Meter Reading

- Home and Building Automation

- Wireless Alarm and Security Systems

- Industrial Monitoring and Control

- Machine to Machine (M2M)

- Internet of Things (IoT)

# 1 Electrical Specifications

### 1.1 Absolute Maximum Ratings

| Parameter                          | Min.     | Max.     | Units |

|------------------------------------|----------|----------|-------|

| Supply Voltage, VDD with Respect   | 0        | 3.8      | V     |

| to GND                             |          |          |       |

| Voltage on any pin with Respect to | GND-0.6V | VDD+0.6V | V     |

| GND and VDD (VDD MAX=3.6V)         |          |          |       |

| Input RF level                     |          | +10      | dBm   |

| Storage temperature range          | -50      | 150      | °C    |

| Maximum soldering temperature      |          | 260      | °C    |

# 1.2 General Operating Conditions

| Parameter                 | Min.     | Тур.     | Max.     | Units | Condition                  |

|---------------------------|----------|----------|----------|-------|----------------------------|

| Power Supply              | 1.8      | 3.3      | 3.6      | V     | (1)                        |

| Operating Temperature     | -30      |          | +70      | Ŝ     |                            |

| Input low-level voltage   |          |          | 0.25*VDD |       | VDD=1.8V-2.7V              |

| Imput low-level voltage   |          |          | 0.3*VDD  |       | VDD=2.7V-3.6V              |

| CDIO Innut high voltage   | 0.7*VDD  |          |          | V     | VDD=1.8V-2.7V              |

| GPIO Input high voltage   | 0.55*VDD |          |          | V     | VDD=2.7V-3.6V              |

| Output low-level voltage  |          | 0.1*Vpd  | 0.2*VDD  |       | VDD>1.8V, IOL max          |

| Output high-level voltage | 0.8*VDD  | 0.9*Vpd  |          |       | VDD>1.8V, IOL max          |

| Input leakage current     | -1       | +/-0.015 | +1       | μΑ    | Pull-up resistors disabled |

(1): Equipment is powered by a circuit (separately approved, not investigated) that is insulated from the mains supply by an insulation not less than that between the primary and secondary circuits of a safety isolating transformer according to IEC 61558-2-6 or equivalent.

The system is considered (only) for the conditions of network environment 0 (see CEI CLC/TR 62102:2006). No over-voltage from telecommunication network possible, no subject to transient over voltages due to atmospheric discharges and faults in power distribution systems. **Max VDD and VRF Ramp Time is 3 ms.**

# 1.3 General Specifications

| Specification                  | Description                                                         |

|--------------------------------|---------------------------------------------------------------------|

| Frequency band                 | 433.050–434.790, 863.000-870.000, 902-928 MHz                       |

| Modulation Method              | FSK, GFSK, and LoRa® Technology modulation                          |

| Maximum Over-the-Air Data Rate | 300 kbps with FSK modulation; 10937 bps with LoRa Technology        |

|                                | modulation                                                          |

| RF Connection                  | Board edge connection                                               |

| Interface                      | UART                                                                |

| Operation Range                | Up to 15 km coverage at suburban; up to 5 km coverage at urban area |

| Sensitivity at 1% PER          | 146 dBm Dependent on modulation settings, Receiver Bandwidth        |

|                                | (RBW), and Spreading Factor (SF).                                   |

| RF TX Power                    | Adjustable up to max. 13 dBm on 433 MHz band; max. 17 dBm on the    |

|                                | 868/915 MHz band                                                    |

# 1.4 Current Consumption

| State      | CPU Mode | I CPU | TRX Mode    | I TRX  | Total | Units    |

|------------|----------|-------|-------------|--------|-------|----------|

| SLEEP      | SLEEP    | 0.590 | SLEEP       | 0.2    | 0.790 | uA       |

| STANDBY    | STANDBY  | 1.2   | SLEEP       | 0.2    | 1.4   | uA       |

| IDLE       | ACTIVE   | 4.5   | SLEEP       | 0.0002 | 4.5   | mA       |

| RX 433 MHz | ACTIVE   | 4.5   | RX          | 11.5   | 16    | mA (TYP) |

| RX 868 MHz | ACTIVE   | 4.5   | RX          | 10.3   | 14.8  | mA (TYP) |

| RX 915 MHz | ACTIVE   | 4.5   | RX          | 11.5   | 14.8  | mA (TYP) |

| TX +13 dBm | ACTIVE   | 4.5   | TX RFO_LF   | 28     | 32.5  | mA (TYP) |

| TX +17 dBm | ACTIVE   | 4.5   | TX PA_BOOST | 90     | 94.5  | mA (TYP) |

The current consumption specifications are derived for the operational condition shown below:

| Condition             | Value   | Unit    |

|-----------------------|---------|---------|

| Supply Voltage        | 3.3     | V       |

| RF Bandwidth          | 125     | kHz     |

| CRC                   | Enabled |         |

| Error Correction Code | 4/6     |         |

| Packet Error Rate     | 1       | %       |

| Payload Lenght        | 64      | Bytes   |

| Preamble Lenght       | 12      | Symbols |

| LNA Boost             | OFF     |         |

| Spreading Factor      | 12      |         |

# 1.5 Transmitted Output Power in LoRa Mode

| Frequency (MHz) | Typical Output Power (dBm) |

|-----------------|----------------------------|

| 433             | 13                         |

| 868             | 17                         |

| 915             | 17                         |

# 1.6 Receiver Sensitivity in LoRa Mode

| Frequency (MHz) | BW (kHz) | SF | Sensitivity | Unit |

|-----------------|----------|----|-------------|------|

| 433             | 7.8      | 12 | -148        |      |

| 868             | 125      | 11 | -133        | dBm  |

| 915             | 125      | 11 | -133        |      |

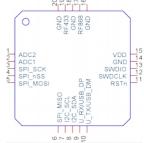

#### 2 PIN-OUT

| PIN#                 | BIT Assigned Function        | Туре                              | Type Optional                                                                                                                                                                                      |         |            |            |  |  |

|----------------------|------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|------------|--|--|

|                      |                              |                                   | UC Pin                                                                                                                                                                                             | Analog  | Timers     | Comm       |  |  |

| 1                    | GPIO0                        | DIG I/O                           | PA08                                                                                                                                                                                               | AIN[16] | TCC1/WO[0] |            |  |  |

| 2                    | GPIO1                        | DIG I/O                           | PA09                                                                                                                                                                                               | AIN[17] | TCC1/WO[1] |            |  |  |

| 3                    | GPIO2                        | DIG I/O                           | PA17                                                                                                                                                                                               |         | TCC2/WO[1] | SPI SCK    |  |  |

| 4                    | GPIO3                        | DIG I/O                           | PA18                                                                                                                                                                                               |         | TCC0/WO[2] | SPI nSS    |  |  |

| 5                    | GPIO4                        | DIG I/O                           | PA16                                                                                                                                                                                               |         | TCC2/WO[0] | SPI MOSI   |  |  |

| 6                    | GPIO5                        | DIG I/O                           | PA19                                                                                                                                                                                               |         | TCC0/WO[3] | SPI MISO   |  |  |

| 7                    | GPIO6 / I2C SCL (1)          | DIG I/O                           | PA23                                                                                                                                                                                               |         |            | I2C SCL    |  |  |

| 8                    | GPIO7 /I2C SDA (1)           | DIG I/O                           | PA22                                                                                                                                                                                               |         |            | I2C SDA    |  |  |

| 9                    | UART RX                      | DIG IN                            | PA25                                                                                                                                                                                               |         |            | USB_DP (2) |  |  |

| 10                   | UART TX                      | DIG OUT                           | PA24                                                                                                                                                                                               |         |            | USB_DM (2) |  |  |

| 11                   | RESETn                       | DIG IN                            | PIG IN  Reset input, active low.To apply an external reset source to this pin, it is required to only drive this pin low during reset, and let the internal pull-up ensure that reset is released. |         |            |            |  |  |

| 12                   | DGB-SWCLK                    | DIG IN                            | PA30                                                                                                                                                                                               |         |            |            |  |  |

| 13                   | DGB-SWDIO                    | DIG I/O PA31                      |                                                                                                                                                                                                    |         |            |            |  |  |

|                      | DGB-3WDIO                    | DIG I/O                           | PA31                                                                                                                                                                                               |         |            |            |  |  |

|                      | GND                          | OV                                | PA31                                                                                                                                                                                               |         |            |            |  |  |

| 14                   |                              |                                   | PA31                                                                                                                                                                                               |         |            |            |  |  |

| 14<br>15             | GND                          | 0V                                | PA31                                                                                                                                                                                               |         |            |            |  |  |

| 14<br>15<br>16       | GND<br>VDD                   | 0V<br>3.3 V IN                    |                                                                                                                                                                                                    |         |            |            |  |  |

| 14<br>15<br>16<br>17 | GND<br>VDD<br>GND            | 0V<br>3.3 V IN<br>0V              |                                                                                                                                                                                                    |         |            |            |  |  |

| 14<br>15<br>16       | GND<br>VDD<br>GND<br>868 ANT | 0V<br>3.3 V IN<br>0V<br>868 MHz F | RF I/O                                                                                                                                                                                             |         |            |            |  |  |

BIT 48LR C

(1) Connect an external EUI-64 Node Identity Chip (MCHP 24A025E64) (2) USB function is available on request as a customization

#### 3 UART Interface

All of the BIT48LR module's settings and commands are transmitted over UART using the ASCII interface. Uart is the standard interface. USB interface is available only for custom design support.

#### 3.1 General characteristics

The default settings for the UART interface are 115200 bps, 8 bits, no parity, 1 Stop bit, no flow control In order to communicate via the UART interface pin P1 (OUT for module) has to be HI and pin P2 (OUT for host) have to be HI.

If host want to send an UART message, it must set the pin P2 to logic HI (for wake-up module) and wait for the module to set pin P1 to logic HI. This can be disabled by pull-up to Vdd on pin P1.

If module has to send an UART message, it must set pin P1 to logic HI (for wake-up host) and wait for the host to set pin P2 to logic HI. This can be disabled by pull-up to Vdd on pin P2.

Any UART message has to be terminated by a carriage return and a new line character ( $\r\$  - 0x0D 0x0A).

#### 3.2 UART API

To issue commands to the BIT48LR module, the user sends keywords followed by optional parameters. Commands (keywords) are case-sensitive, and spaces must not be used in parameters. Hex input data can be uppercase or lowercase. String text data, such as OTAA used for the join procedure, can be uppercase or

lowercase

The use of shorthand for parameters is *NOT* supported.

Depending on the command, the parameter may expect values in either decimal or hexadecimal form; refer to the command description for the expected form. For example, when configuring the frequency, the command expects a decimal value in Hertz such as 868100000 (868.1 MHz). Alternatively, when configuring the LoRaWAN device address, the hex value is entered into the parameter as <code>aabbccdd</code>. To enter a number in hex form, use the value directly. For example, the hex value 0xFF would be entered as FF.

#### 3.3 UART Command table

There are three general command categories, as shown in Table 2-1.

**TABLE 2-1: COMMAND TYPES**

| Command Type                              | Keyword         | Description                                                                                                                                       |

|-------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| System                                    | <sys></sys>     | Issues system level behavior actions, gathers status information on the firmware and hardware version, or accesses the module user EEPROM memory. |

| LoRaWAN™ Class A<br>and Class C Protocols | <mac></mac>     | Issues LoRaWAN Class A and Class C protocols network communication behaviors, actions and configuration commands.                                 |

| Transceiver commands                      | <radio></radio> | Issues radio specific configurations, directly accessing and updating the transceiver setup.                                                      |

See "BIT48LR LoRa® Technology Module Command Reference User's Guide" for a detailed description.

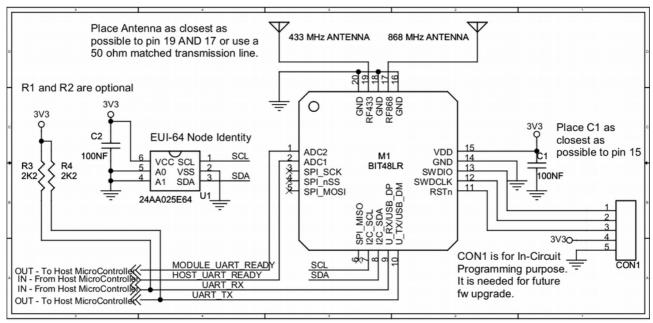

### 4 Typical Application

#### 4.1 Product customization

There are 10 I/O available (1 UART or USB, 1 I2C, 1 SPI, 2 ADC).

Ask us if you want to customize the module or if you want to develop your own application with the use of all the available I/O. The MCU on board is MICROCHIP SAM R34/R35 (ultra-low power microcontroller combined with a UHF transceiver). Please contact the Distributors closest to you for further information.

Leave unused pins unconnected.

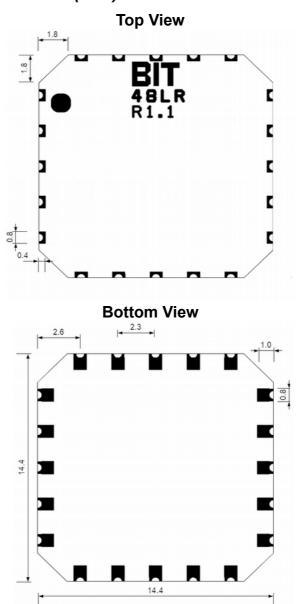

# 5 Mechanical Dimension (mm)

# 6 Soldering profile Recommendation

JEDEC standard IPC/JEDEC J-STD-020D.1 (page 7 and 8), Pb-Free Assembly is recommended.

The standard requires that the heat dissipated in the "surroundings" on the PCB is taken into account. The peak temperature should be adjusted so that it is within the window specified in the standard for the actual motherboard.

Aperture for paste stencil is normally areal-reduced by 20-35%, please consult your production facility for best experience aperture reduction. Nominal stencil thickness of 0.1-0.12 mm recommended.

# 7 Packaging Information

| Orderable device | Status | Package<br>Type | Pins | Package Qty | Eco Plan                | MSL Peak Temp       |

|------------------|--------|-----------------|------|-------------|-------------------------|---------------------|

| BIT48LR          | ACTIVE | MLF             | 20   | 96          | Green (RoHS & no Sb/Br) | Level-2-260C-1 YEAR |

#### 8 General Information

#### 8.1 Disclaimer

B.I.T. srl believes the information contained herein is correct and accurate at the time of this printing. However, B.I.T. srl reserves the right to make changes to this product without notice. B.I.T. srl does not assume any responsibility for the use of the described product; neither does it convey any license under its patent rights, or the rights of others. The latest updates are available at the BIT website or by contacting BIT directly.

As far as possible, major changes of product specifications and functionality, will be stated in product specific Errata Notes published at the BIT website. Customers are encouraged to sign up to the Developers Newsletter for the most recent updates on products and support tools.

Compliance with regulations is dependent on complete system performance. It is the customer's responsibility to ensure that the system complies with regulations.

### 8.2 Life Support Policy

This BIT product is not designed for use in life support appliances, devices, or other systems where malfunction can reasonably be expected to result in significant personal injury to the user, or as a critical component in any life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. B.I.T. srl customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify B.I.T. srl for any damages resulting from any improper use or sale.

#### **Revision list**

| Revision | Data       | Description                 | Fw Version |

|----------|------------|-----------------------------|------------|

| 00.90    | 2019-07-19 | Changed some pin definition | 0.9.b      |

| 00.01    | 2018-12-13 | First Release               | 0.1.b      |

Bit is Italian Technology S.r.l.

Via Luigi Settembrini, 29 – 20020 Lainate (MI)

Tel.: (+39) 02 30465311, fax: (+39) 0230465396

<a href="http://www.bit.it/">http://www.bit.it/</a> info@bit.it